# 155- and 213-GHz AlInAs/GaInAs/InP HEMT MMIC Oscillators

Steven E. Rosenbaum, Brian K. Kormanyos, Linda M. Jelloian, Mehran Matloubian, *Member, IEEE*, April S. Brown, *Senior Member, IEEE*, Lawrence E. Larson, *Senior Member, IEEE*, Loi D. Nguyen, *Member, IEEE*, Mark A. Thompson, Linda P. B. Katehi, *Senior Member, IEEE*, and Gabriel M. Rebeiz, *Senior Member, IEEE*

**Abstract**—We report on the design and measurement of monolithic 155- and 213-GHz quasi-optical oscillators using AlInAs/GaInAs/InP HEMT's. These results are believed to be the highest frequency three-terminal oscillators reported to date. The indium concentration in the channel was 80% for high sheet charge and mobility. The HEMT gates were fabricated with self-aligned sub-tenth-micrometer electron-beam techniques to achieve gate lengths on the order of 50 nm and drain-source spacing of 0.25  $\mu$ m. Planar antennas were integrated into the fabrication process resulting in a compact and efficient quasi-optical Monolithic Millimeter-wave Integrated Circuit (MMIC) oscillator.

## I. INTRODUCTION

THE POTENTIAL of AlInAs/GaInAs High Electron Mobility Transistors (HEMT's) on InP substrates has been investigated extensively for low-noise and power applications at millimeter-wave frequencies (30–100 GHz), and the recent developments in HEMT materials growth [1], layer scaling [2], and electron-beam fabrication [3], have resulted in the fabrication of the world's highest cutoff frequency ( $f_t$ ) transistors [4]. We have combined the AlInAs/GaInAs technology with integrated antennas to build a millimeter-wave quasi-optical oscillator. The design is based on the coplanar waveguide (CPW)-fed quasi-optical slot oscillators which has been investigated by Kormanyos [5], [6] and Moyer [7]. The uniplanar circuit requires no via holes and no backing ground plane and is compatible with the monolithic integration of high speed transistors. With the uniplanar approach, it is possible to put the InP oscillator on a high-resistivity silicon dielectric lens (silicon and InP have similar dielectric constants). The substrate lens simulates an infinite dielectric medium, eliminates power loss to substrate modes and makes the pattern nearly

Manuscript received July 6, 1994; revised November 15, 1994. This work was supported by the US Airforce Rome Laboratory, Manscom Air Force Base, under the direction of Dr. Paul Carr and Mr. Richard Webster under Contract F19628-90-C-0171 and the NASA Center for Space Terahertz Technology at the University of Michigan.

S. E. Rosenbaum, L. M. Jelloian, M. Matloubian, L. E. Larson, L. Nguyen, and M. A. Thompson are with the Hughes Malibu Research Laboratories, Malibu, CA 90265 USA.

B. K. Kormanyos was with the University of Michigan. He is now with Hughes Space and Communications Group, Los Angeles, CA 90009 USA.

A. S. Brown was with the Hughes Malibu Research Laboratories, Malibu, CA 90265 USA. She is now with the Georgia Institute of Technology, Atlanta, GA USA.

L. P. B. Katehi and G. M. Rebeiz are with the Electrical Engineering and Computer Science Department, The University of Michigan, Ann Arbor, MI 48109-2122 USA.

IEEE Log Number 9409120.

uni-directional [8]. Perhaps, the most important advantage of this approach is that the different designs at 150–550 GHz are independent of the substrate height and can all be integrated together on the same chip. This considerably reduces the fabrication time and cost per oscillator unit. The slot antenna impedance in this environment is accurately calculated using the space domain integral equation technique [9], and will not be discussed in this paper. Using this technique, we have succeeded in building 155- and 213-GHz oscillators while the maximum previously reported transistor oscillator performance has been limited to 131 GHz [10].

## II. MATERIALS DEVELOPMENT AND OSCILLATOR FABRICATION

The epitaxial layers used in this work were grown in a Riber 2300 molecular-beam epitaxy (MBE) system, typically at a substrate temperature of 500°C, a growth rate of 600 nm/h, and a V/III beam equivalent pressure ratio of 40. Further details of these standard growth conditions can be found in [1]. Fig. 1 shows a diagram of the layer structure of the MBE material. The growth of the delta-doped, strained layer structures deviates from the standard conditions in several ways. The first is a reduction of the substrate temperature to 320°C, during and after the growth of the delta-doped layer in order to minimize the surface segregation of silicon atoms in AlInAs. By controlling the growth temperature in this fashion, we are able to improve the abruptness of the silicon profile and achieve an increase of approximately 20–30% in electron transfer efficiency [4]. The second modification is the use of a wider spacer thickness. In order to obtain a high mobility using delta doping, we increased the spacer thickness of the delta-doped structures from 2–6 nm. The last, but most important, is a lower substrate temperature during the growth of the pseudomorphic channel. We grew this layer at a substrate temperature of 440°C, as opposed to the standard 500°C, to prevent three-dimensional nucleation and misfit dislocation production. The resulting sheet charge and mobility were approximately  $2.7 \times 10^{12} \text{ cm}^{-2}$  and  $13000 \text{ cm}^2/\text{V}\cdot\text{s}$ , respectively.

We employed a self-aligned-gate (SAG) process first proposed by Mishra *et al.* [12], which consists of five levels: 1) alignment marks, 2) device isolation, 3) T-shaped gate definition, recess, and metalization (Ti/Pt/Au), 4) ohmic definition, metalization (AuGe/Ni/Au) with the T-shaped gate serving as a shadow mask, and alloying, and finally, 5)

|                            |        |

|----------------------------|--------|

| GalnAs: Si Cap             | 70 Å   |

| AlInAs Schottky            | 200 Å  |

| AlInAs Spacer              | 60 Å   |

| GalnAs Channel             |        |

| 80 Å 80% In                | 200 Å  |

| 125 Å lattice-matched      |        |

| AlInAs/GalnAs superlattice | ~400 Å |

| AlInAs Buffer              | 2500 Å |

#### InP Substrate

Fig. 1. Layer structure of the InP MBE material.

Fig. 2. Cross-section of 50-nm T-shaped gate.

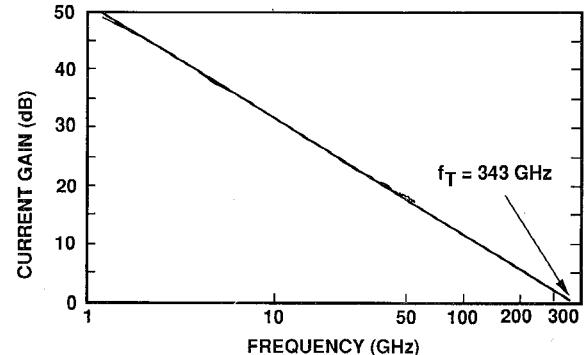

overlay. We defined the sub-0.1- $\mu\text{m}$  gates in a bi-layer of PMMA/P(MMA-MAA) electron-beam resist using a Phillips EBPG-4 electron-beam lithography system operating at 50-kV acceleration voltage. The resulting drain-to-source spacing is approximately 0.25  $\mu\text{m}$ . Fig. 2 shows the cross-section of a 50-nm T-shaped gate after the deposition of the self-aligned ohmic metal. The addition of the ohmic metal reduces its resistance from approximately 1500–1000  $\Omega/\text{mm}$ , which is the lowest resistance ever reported for a 50-nm-long gate [4]. Typical peak extrinsic transconductance for the final wafer lot was approximately 1400 mS/mm for a 50- $\mu\text{m}$  device measured after all the MMIC fabrication steps, with an associated *extrinsic* short-circuit current-gain extrapolated cutoff frequency,  $f_T$ , of approximately 340 GHz (Fig. 3). The extrapolated maximum oscillation frequency ( $f_{\max}$ ) at  $-6$  dB/octave for an *intrinsic* 50- $\mu\text{m}$  device is 740 GHz.

The processing of the circuits begins with the ohmic contacts, other than the device ohmics, which are defined by lifting off AuGe-Ni-Au metallurgy. Second is the isolation implant, used to define the active area of the transistors, achieved by use of boron ions. Next is the self-aligned-gate (SAG) process, which is described above, followed by the device ohmic step, wherein the gate itself acts as a mask for the ohmic metal,

Fig. 3. HEMT short-circuit current gain versus frequency. The measurements are made to 50 GHz and extrapolated thereafter.

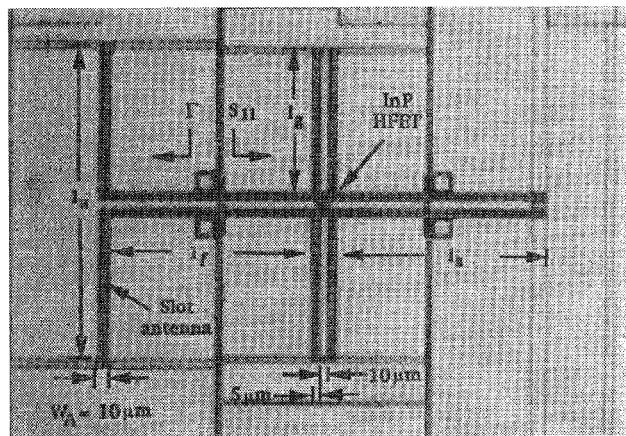

Fig. 4. The fabricated InP 155-GHz MMIC oscillator. The slot antenna is to the left. The dark areas outline the InP substrate.

also described in the previous section. Next is the perimeter etch, where we etch down to the InP substrate everywhere except in the device itself, to provide a very high resistance dielectric for the slot antenna and the CPW transmission line. DC biasing of the transistor is made possible by slits in the ground plane which isolate the gate, drain and source (see Fig. 4 for the completed MMIC oscillator). These slits are capacitively bypassed to create an uninterrupted ground plane for the RF circuit. Following that is the metal overlay, which defines the device electrodes, the transmission lines, slot antennas and the ground planes. Then, the capacitor dielectric layer is formed. The dielectric material is 0.22  $\mu\text{m}$  of silicon monoxide (SiO). The post-metal fabrication step then defines the top plates and, hence, the size of the capacitors. Finally, the span metal step is used to fabricate the air-bridges from the capacitors as well as the plated metal on the transmission lines and ground plane.

### III. OSCILLATOR DESIGN

The oscillator design follows the reflection amplifier approach presented in [12]. Computer optimization is applied at the source and gate terminals to maximize the reflection coefficient at the gate of the device which is connected to the slot antenna. The antenna impedance is used as a parameter in the oscillator design, and therefore the matching networks

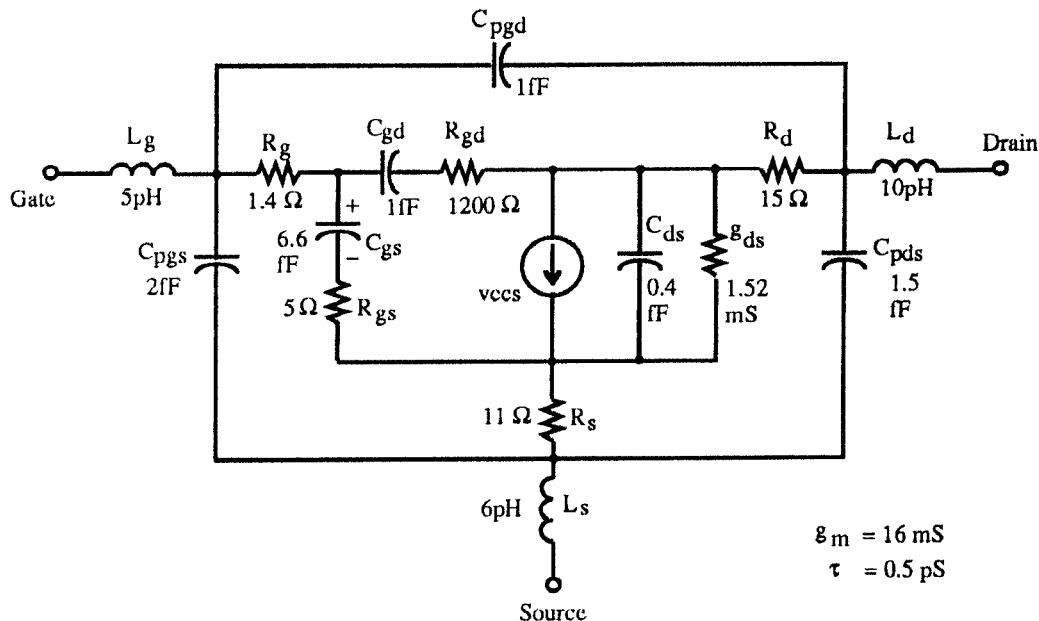

Fig. 5. Fitted small signal model for the scaled InP based HEMT with  $0.05\text{-}\mu\text{m}$  gate length and  $10\text{-}\mu\text{m}$  gate width (see text).

TABLE I

DESIGN PARAMETERS FOR THE TWO SUCCESSFUL MONOLITHIC MILLIMETER-WAVE OSCILLATORS. THE VALUES  $L_g, \dots$  ARE DEFINED IN FIG. 4

| $F^*$<br>(GHz) | $L_p, C_p^{**}$ | $g_m$<br>(mS) | $l_s$<br>( $\mu\text{m}$ ) | $l_g$<br>( $\mu\text{m}$ ) | $l_f$<br>( $\mu\text{m}$ ) | $l_a^{**}$<br>( $\mu\text{m}$ ) | $1/S_{11}$<br>(mag, ang) | $\Gamma$<br>(mag, ang) |

|----------------|-----------------|---------------|----------------------------|----------------------------|----------------------------|---------------------------------|--------------------------|------------------------|

| 150            | High            | 10            | 239                        | 164.5                      | 230.5                      | 360                             | 0.188, 164.4             | 0.595, 164             |

| 500            | High            | 16            | 107                        | 86.5                       | 71                         | 70                              | 0.323, -147              | 0.897, -146.5          |

are minimized. This results in an oscillator circuit that is much smaller than a wavelength, typically  $400\text{ }\mu\text{m}$ -square at 150 GHz and  $100\text{ }\mu\text{m}$ -square at 500 GHz. All of the cpw lines in the oscillator design have a center conductor width of  $10\text{ }\mu\text{m}$  and  $5\text{ }\mu\text{m}$  gap giving an impedance of approximately  $50\text{ }\Omega$  and an effective dielectric constant of 6.7 on an InP substrate (calculated from a full-wave model). The loss in the cpw lines was taken into account in the design procedure and was estimated by extrapolating the data presented in [13]. A conservative value of  $0.67\text{ dB/mm}$  at 60 GHz scaled with the square root of the frequency was used. The InP HEMT transistor has a  $10\text{ }\mu\text{m}$  gate-width to result in favorable impedance levels at 150–500 GHz and to fit directly in the center conductor of the cpw line. This eliminates the need to model discontinuities in the cpw line at millimeter-wave frequencies.

Oscillator designs were carried out at frequencies from 150–550 GHz. To obtain a small signal model for the  $10\text{-}\mu\text{m}$  transistor, a larger device with a  $50\text{ }\mu\text{m}$  gatewidth was built and tested to 50 GHz (Fig. 3). The parasitics of the  $50\text{-}\mu\text{m}$  device were stripped off and an intrinsic model was obtained for the  $50\text{-}\mu\text{m}$  device. This intrinsic model was mathematically scaled to obtain the equivalent intrinsic model of the smaller  $10\text{-}\mu\text{m}$  device (Fig. 5). The parasitic capacitances and inductances for the  $10\text{-}\mu\text{m}$  model were determined using quasi-static techniques and the geometry of the  $10\mu\text{m}$  device. Since this model was derived from measurements on a  $50\text{-}\mu\text{m}$  device, a

large uncertainty exists in the  $10\text{-}\mu\text{m}$  device model parameters. The parasitic elements  $L_g$ ,  $L_d$ ,  $L_s$ ,  $C_{pgs}$ ,  $C_{pgd}$ , and  $C_{pds}$  associated with the extrinsic contact metalizations are known to about  $\pm 4\text{ pH}$  or  $\text{fF}$ . Also, values of the intrinsic elements  $R_{gs}$ ,  $C_{gs}$ ,  $R_{gd}$ ,  $C_{gd}$ ,  $g_m$ ,  $\tau$ ,  $C_{ds}$ , and  $g_{ds}$  are thought to be accurate to  $\pm 20\%$ . No independent confirmation of these estimates could be made since no S-parameter measurements were made on a  $10\text{ }\mu\text{m}$  device.

We decided to “bracket” the oscillator designs. Due to the uncertainty existing in the device model, several designs were done at each frequency. The cases considered were with parasitics at their nominal values (Low) and at twice these values (High). The intrinsic transconductance was also taken to be either  $16\text{ mS}$  (nominal) or  $10\text{ mS}$  (low). This resulted in 16 different designs covering the range of 150–550 GHz. The idea behind the above choices is that the parasitics at 150 GHz and above will be higher than these predicted by 50-GHz measurements due to charge accumulation at the edges of the conductors. The low value of the intrinsic  $g_m$  of  $10\text{ mS}$  was chosen because it fits the DC measurements closer than the small-signal 50-GHz extrapolated value of  $16\text{ mS}$ .

#### IV. MILLIMETER-WAVE MEASUREMENTS

The InP chip containing all the oscillators from 150–550 GHz was positioned on a  $2.54\text{-cm}$ -diameter elliptical silicon substrate lens for testing purposes and dc bias was applied to the oscillator-under-test using micropositioner dc probes. The

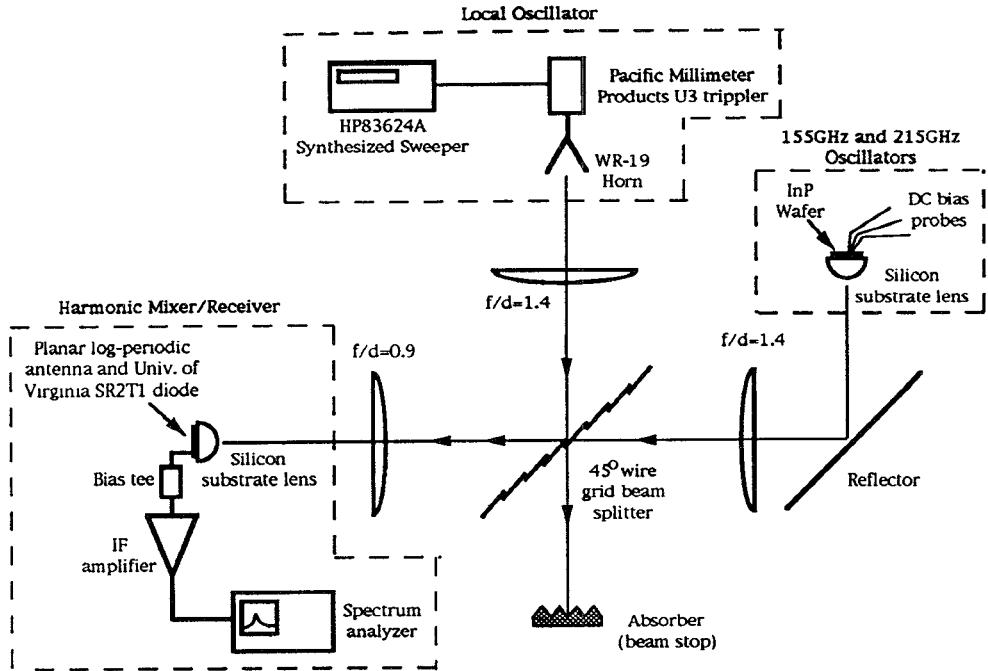

Fig. 6. Wideband quasi-optical harmonic mixer setup for accurate frequency determination and spectrum measurements.

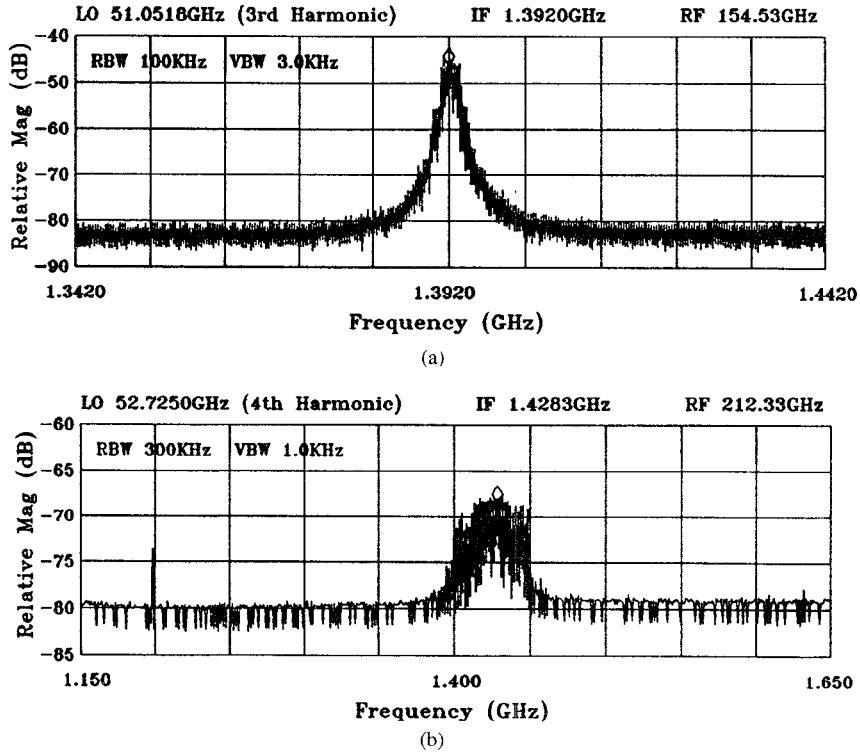

Fig. 7. Measured down converted spectra of the (a) 155- and (b) 213-GHz oscillators.

millimeter-wave signal radiates from the lens to the quasi-optical measurement setup. There are no critical dimensions to control for the different test frequencies (oscillators) and this leads to a very simple test setup. Rough frequency measurements were obtained by aligning the silicon substrate in front of an InSb hot electron bolometer with an interferometer and mechanical chopper in the beam path. Two of the designs were found to oscillate with about 90% yield (Table I). The

150-GHz design case assuming high parasitics and 10 mS transconductance (150.H.10) oscillated near its design frequency generating an output signal at 155 GHz. The 500-GHz case assuming high parasitics and 16 mS transconductance (500.H.16) generated an output at an unexpected frequency near 213 GHz. The other 14 cases generated no output. This situation is not surprising considering the large uncertainty which exists in the 10- $\mu$ m device model.

The oscillator frequencies were accurately measured and their spectrums were observed using a quasi-optical wideband harmonic mixer setup (Fig. 6). The harmonic mixer uses a back-to-back Schottky diode at the apex of a wideband log-periodic antenna. The antenna is placed on a substrate lens to eliminate power loss to substrate modes. The harmonic mixer is pumped quasi-optically at 37–50 GHz (LO) thus resulting in a low conversion loss at 150–200 GHz (RF) [14]. A 45° beam splitter is used as a wideband diplexer for the LO and RF signal. The diplexer introduces a 3-dB loss in the LO and RF signal paths, but this is not detrimental for spectrum measurements. The measured down-converted spectrums of a 155- and a 213-GHz oscillator are shown in Fig. 7. The LO frequency was varied to observe both upper and lower sidebands and different IF frequencies were used to insure that the harmonic numbers and RF frequencies are correctly determined. To be certain that the observed signal corresponds to the fundamental oscillation frequency, the LO was adjusted to search for any signals at 1/2 and 1/3 of the oscillator frequency and no signals were observed.

The oscillator output power was estimated with a quasi-optical setup using calibrated waveguide diode detectors and a lock-in amplifier. The slot-oscillator power is determined from the amplitude of the received signal at the calibrated detector, the gain of the receiving horn antenna (23 dB), the directivity of the transmitting slot/lens antenna and by using the Friis transmission equation. The aperture efficiency of the slot oscillator on a substrate lens is 40%. This has been determined earlier from pattern measurements of a single slot antenna on a silicon substrate lens at 20 GHz [5] and includes the lens-air reflection loss of 1.9 dB. It is estimated that the maximum error in the power calculation is 25% with a 15% contribution from the calibrated waveguide detector and a  $\pm 10\%$  contribution from the slot/lens antenna directivity. The total output power is found to be no less than  $10\text{-}\mu\text{W}$  ( $\pm 25\%$ ) for the 155-GHz oscillator and no less than  $1\text{ }\mu\text{W}$  for the 213-GHz oscillator. The corresponding (minimum) dc to RF efficiencies are 0.13% at 155 GHz and 0.014% at 215 GHz. The 155-GHz power measurements are consistent with the fact that the transistor is very small with only a  $10\text{-}\mu\text{m}$  gate width. The circuits were optimized for high loop gain and not maximum power, and there is a lot of uncertainty in the  $10\text{-}\mu\text{m}$  device model. Also, the associated *extrinsic* short-circuit current-gain cutoff frequency ( $f_t$ ) for a  $10\text{-}\mu\text{m}$  transistor with high parasitics and low  $g_m$  is 135 GHz and the associated extrapolated maximum oscillation frequency ( $f_{\max}$ ) is 400 GHz.

## V. CONCLUSION

This paper presents the highest frequency achieved to-date for a InP millimeter-wave three-terminal device. Additional time spent on the modeling of these transistors could lead to better circuit designs that will enable this same technology to yield oscillators at 300 GHz and above. The inclusion of a cpw-fed planar slot antenna in the oscillator design enabled the fabrication of a large number of oscillators on a single InP chip and resulted in an easy system for testing purposes. A large number of these devices could be integrated together in quasi-optical power combining designs at millimeter wave frequen-

cies to generate milliwatt power levels [15]. The successful development of these monolithic oscillators demonstrates the high frequency capabilities of the sub-micron gate InP based HEMT's which should also find applications as small signal millimeter-wave and submillimeter-wave amplifiers.

## ACKNOWLEDGMENT

The authors acknowledge the support of Drs. R. Webster and P. Carr of the Air Force Rome Laboratory.

## REFERENCES

- [1] A. S. Brown, U. K. Mishra, J. A. Henige, and M. J. Delaney, "The impact of epitaxial layer design and quality on GaInAs/AlInAs high electron mobility transistor performance," *J. Vac. Sci. Technol.*, vol. B6, no. 2, Mar./Apr. 1988.

- [2] L. D. Nguyen, A. S. Brown, M. J. Delaney, U. K. Mishra, L. E. Larson, L. M. Jelloian, M. E. Melendes, C. Hooper, and M. Thompson, "Vertical scaling of ultrahigh-speed AlInAs/GaInAs HEMT's," in *IEDM Tech. Dig.*, Dec. 1990, pp. 105–108.

- [3] L. D. Nguyen, L. M. Jelloian, M. A. Thompson, and M. Lui, "Fabrication of an 80-nm self-aligned T-gate AlInAs/GaInAs HEMT," in *IEDM Tech. Dig.*, Dec. 1990, pp. 101–104.

- [4] L. D. Nguyen, A. S. Brown, M. A. Thompson, and L. M. Jelloian, "50-nm self-aligned-gate pseudomorphic AlInAs/GaInAs high electron mobility transistors," *IEEE Trans. Electron Dev.*, vol. 39, pp. 2007–2014, Sept. 1992.

- [5] B. K. Kormanyos, W. Harokopus Jr., L. P. B. Katehi, and G. M. Rebeiz, "CPW-Fed active slot-antennas," *IEEE Trans. Microwave Theory Tech.*, vol. 42, pp. 541–545, Apr. 1994.

- [6] B. K. Kormanyos, S. E. Rosenbaum, L. P. Katehi, and G. M. Rebeiz, "Monolithic 155 GHz and 215 GHz Quasi-Optical Slot Oscillators," in *IEEE Microwave Theory Tech. Soc. Int. Microwave Symp. Tech. Dig.*, May 23–27, 1994, pp. 835–838.

- [7] H. P. Moyer and R. A. York, "Active cavity backed slot antenna using MESFET's," *IEEE Microwave and Guided Wave Lett.*, vol. 3, Apr. 1993.

- [8] G. M. Rebeiz, "Millimeter-wave and terahertz integrated circuit antennas," *Proc. IEEE*, vol. 80, pp. 1748–1770, Nov. 1992.

- [9] N. I. Dib and P. B. Katehi, "Modeling of shielded CPW discontinuities using the space domain integral equation method (SDIE)," *J. Electromag. Waves and Appl.*, vol. 5, no. 4/5, pp. 503–523, 1991.

- [10] Y. Kwon, D. Pavlidis, T. Brock, and D. Streit, "A D-band monolithic fundamental oscillator using InP-based HEMT's," *IEEE Trans. Microwave Theory Tech.*, vol. 37, pp. 2336–2344, Dec. 1993.

- [11] U. K. Mishra, A. S. Brown, L. M. Jelloian, M. Thompson, L. D. Nguyen, and S. E. Rosenbaum, "Novel high performance self-aligned 0.1-mm long T-gate AlInAs-GaInAs HEMT's," in *IEDM Tech. Dig.*, Dec. 1989, pp. 101–104.

- [12] G. R. Basawapatna and R. B. Staciff, "A unified approach to the design of wide-band microwave solid-state oscillators," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-27, pp. 379–385, May 1979.

- [13] W. H. Haydl *et al.*, "Attenuation of millimeter-wave coplanar lines on GaAs and InP over the range 1–60 GHz," in *IEEE Microwave Theory Tech. Soc. Int. Microwave Symp. Tech. Dig.*, 1992, pp. 369–352.

- [14] B. K. Kormanyos and G. M. Rebeiz, "A 26–220 GHz harmonic mixer-receiver," *Microwave J.*, vol. 36, no. 7, pp. 103–108, July 1993.

- [15] ———, "20 GHz power combining slot—Oscillator array," *IEEE Microwave and Guided Wave Lett.*, vol. 4, July 1994.

**Steven E. Rosenbaum** received the B.S. degree from the University of Michigan, Ann Arbor, in 1983, and the M.S. degree from the University of California, Los Angeles, in 1989.

Since joining the Hughes Aircraft Company in 1983 and the Hughes Research Laboratories in 1985, he has made fundamental contributions to the design of microwave and millimeter-wave integrated circuits (MMIC's) using InP-based high electron mobility transistors (HEMT's). He is currently a senior research staff member and is responsible for the design and testing of HEMT and heterojunction-bipolar transistor MMIC's.

**Brian K. Kormanyos** received the B.S. degree in electrical engineering from the University of Washington, Seattle, and the Ph.D. degree from the University of Michigan, Ann Arbor, in applied electromagnetics and solid-state devices, in 1989 and 1994, respectively.

His research interests are in microwave and millimeter-wave circuits and in high-frequency (VHF, UHF cellular communication) analog circuit design. He is currently a member of the technical staff at Hughes Space and Communications Group, Los Angeles, CA.

**Linda M. Jolloian** received the B.S. and M.B.A. degrees from Pepperdine University, Malibu, CA, in 1982 and 1986, respectively.

Since joining Hughes Research Laboratories in 1982, she has been involved with process development and fabrication of GaAs MESFET's, GaAs/AlGaAs HEMT's, and InAlAs/GaInAs HEMT's for low-noise amplification at millimeter-wave frequencies. She is currently a member of the research staff.

**Mehran Matloubian** (S'85-M'85-S'86-M'89), received the B.S., M.S., and Ph.D. degrees from the University of California, Los Angeles in 1983, 1985, and 1989, respectively.

Since joining the Hughes Research Laboratories in 1990, he has been responsible for the development of AlInAs/InGaAs (on InP) HEMT's for millimeter-wave power amplifiers, and for the design of millimeter-wave monolithic integrated circuits. Prior to joining the Research Laboratories, he had experience working on microwave and millimeter-wave characterization of transistors and dielectric materials.

Dr. Matloubian is a member of Phi Beta Kappa, Eta Kappa Nu, and Tau Beta Pi.

**April S. Brown** (S'79-M'81-M'87-*SM'91*), received the B.S. degree in 1981 from North Carolina State University, and the M.S. and Ph.D. degrees from Cornell University, Ithaca, NY, in 1984 and 1985, respectively.

After joining the Hughes Research Laboratories in 1986, she was responsible for material development and research related to HEMT devices and circuits. She was an assistant professor at the University of Michigan during the 1985-1986 academic year, where she worked on the growth and characterization of InP-based compounds. She was a physicist at the Army Research Office from 1988 to 1989, where she monitored programs in condensed matter physics. She is currently an associate professor at the Georgia Institute of Technology, Atlanta, GA.

**Lawrence E. Larson** (M'82-S'82-M'86-*SM'90*), received the B.S. and M.S. degrees from Cornell University, Ithaca, NY, in 1979 and 1980, and the Ph.D. degree from the University of California, Los Angeles, in 1986, all in electrical engineering.

He has been with Hughes Research Laboratories, Malibu, CA, since 1984, where he has been engaged in research into advanced high-speed semiconductor devices and circuits. He is currently Manager of the Telecommunications Technology Department in the Microwave Devices and Circuits Research Laboratory. He has been a program manager on a number of Hughes and government programs that have advanced the state of the art in high-speed semiconductors, and was assistant program manager on the Hughes/ARPA MIMIC Program from 1992-1994. In addition, he was an associate adjunct professor at UCLA from 1990-1993. He has published over 80 papers and has over a dozen U.S. Patents.

Dr. Larson is a member of Sigma Xi and Eta Kappa Nu.

**Loi D. Nguyen** (S'83-S'84-M'84-*M'89*), received the A.S. degree in engineering science from Broome Community College, Binghamton, NY, in 1982, and the B.S. and Ph.D. degrees in electrical engineering from Cornell University, Ithaca, NY, in 1984 and 1989, respectively.

Since joining Hughes Research Laboratories in 1988, he has made fundamental contributions to the design and fabrication of ultrashort gate length InP-based HEMT's. He is currently the Manager of the HEMT Technology Department and is responsible for the research and development, as well as prototype production, of HEMT devices and circuits for microwave and millimeter-wave applications. He has written or contributed to approximately 40 publications and holds two patents in the field of compound semiconductor materials and devices.

**Mark A. Thompson** received the diploma in electrical engineering technology from Denver Institute of Technology, Denver, CO, in 1977.

Since joining Hughes Research Laboratories in 1986, he has made significant contributions to the development and fabrication of ultrashort gate length FET's and HEMT's. He is currently responsible for the electron-beam lithography system at Hughes, as well as the development and implementation of advanced electron-beam lithography processes. His work in this area has led to the successful fabrication of a deep sub-micron, self-aligned-gate HEMT with a record  $f_T$  of over 340 GHz, the process for which he presently holds a patent. Prior to his employment with Hughes, he was with Texas Instruments. From 1977 to 1986, he performed failure analysis on MOS memories and contributed to the process and product development of Advanced Schottky and Advanced Low Power Schottky LSI and VLSI integrated circuits, programmable array logic (PAL) circuits and Bipolar-Complementary MOS (BiCMOS) integrated circuits. He has authored or contributed to over 20 publications in the fabrication of compound semiconductor devices and circuits.

**Linda P. B. Katehi** (S'81-M'84-*SM'89*), for a biography, see p. 83 of the January 1994 issue of this *TRANSACTIONS*.

**Gabriel M. Rebeiz**, (S'86-M'88-*SM'93*), for a biography, see page 545 of the April 1994 issue of this *TRANSACTIONS*.